导读:第一块芯片背后的故事。

在1971年1月份的一个傍晚,6点左右,同事们都正常下班,回家嗨去了。范金却收到了工艺制造部门发来的晶圆,既心潮澎湃,又忧心忡忡。虽然拿晶圆的手稍稍有些颤抖 ,但是范金毕竟久经沙场,他按部就班完成晶圆测试准备工作,终于上电那一刻到来了,仿佛整个世界都停止了呼吸,他的心也提到了嗓子眼。好吧,其实没有什么悬念,芯片点亮了!他趁热打铁,一直奋战到凌晨3点,既筋疲力竭,又激动不已,激动的是芯片PPA都一切正常。他无比轻松地回到家中,与妻子分享了他此刻的喜悦......

这其实就是英特尔第一款微处理器芯片4004 Bringup的过程,相信每一个经过了Bringup工作的芯片工程师都会有类似的心路历程。4004芯片其实是Intel接到的一个外包项目,客户是日本的Busicom公司,主要是用在电子计算器上,为什么取名4004呢?其中第一个“4”代表此芯片是客户订购的产品编号,后一个“4”代表此芯片是英特尔公司制作的第四个订制芯片,还有4001,4002,4003。四颗芯片统称为MCS-4家族。

在介绍芯片如何设计之前,先介绍一下这个项目中的两个重要人物,本篇的主人公主要是范金:

架构设计负责人:霍夫(Ted Hoff)

将CPU的控制电路和运算电路巧妙地整合在一起,把两个存储芯片附加上去,一个存储数据,另一个存储CPU指令程序,大大降低了成本。

电路设计负责人:范金(Federico Faggin)

英特尔CEO诺伊斯,从老东家仙童公司挖过来,1970年4月加入Intel,负责4001-4004四款芯片的设计工作。包括工艺选型,逻辑和电路设计,版图和布局布线设计,测试方案设计,测试程序开发等等,是个扛把子。

工艺选型

在仙童工作时,范金就发明了一种自校准的Silicon Gate MOS管工艺技术,相比传统的Aluminum Gate MOS管工艺技术,晶体管密度可以更高,功耗和面积更有优势,并且成本更低,可靠性更高。

范金来到Intel设计4004时,选用的就是这种nMOS工艺,并且做了一些工艺改进。当时Intel有两英寸的晶圆制造产线,光刻机采用的光源是汞灯,但是掩膜(Mask)的制作需要靠手工和放大镜,如下图所示:

手工Mask制作

逻辑和电路设计

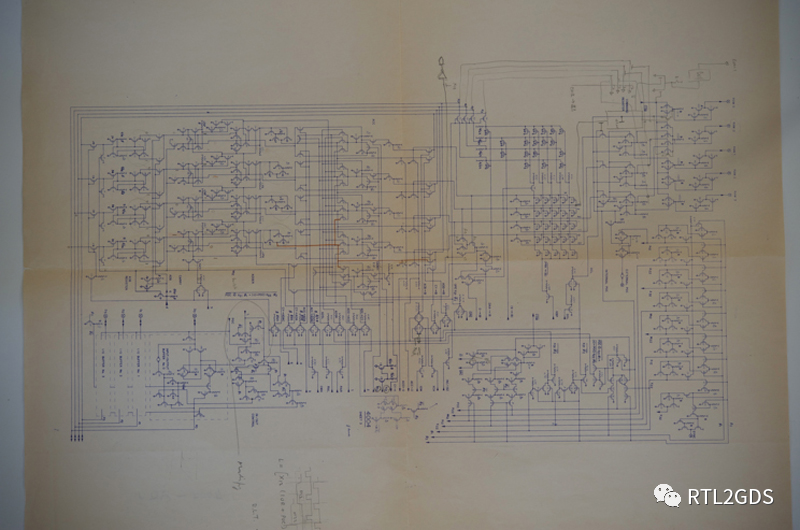

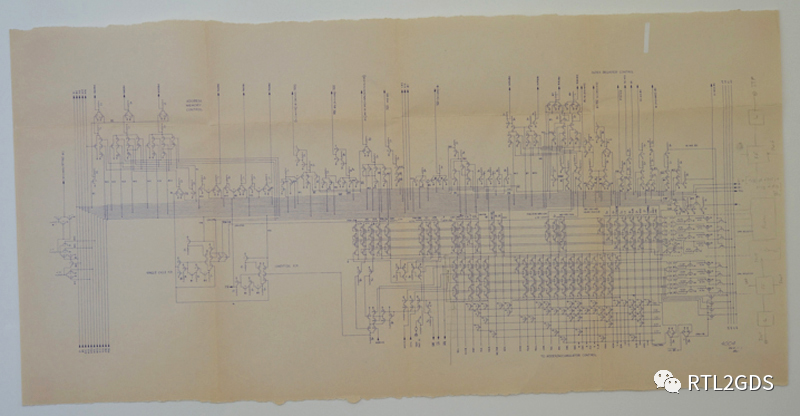

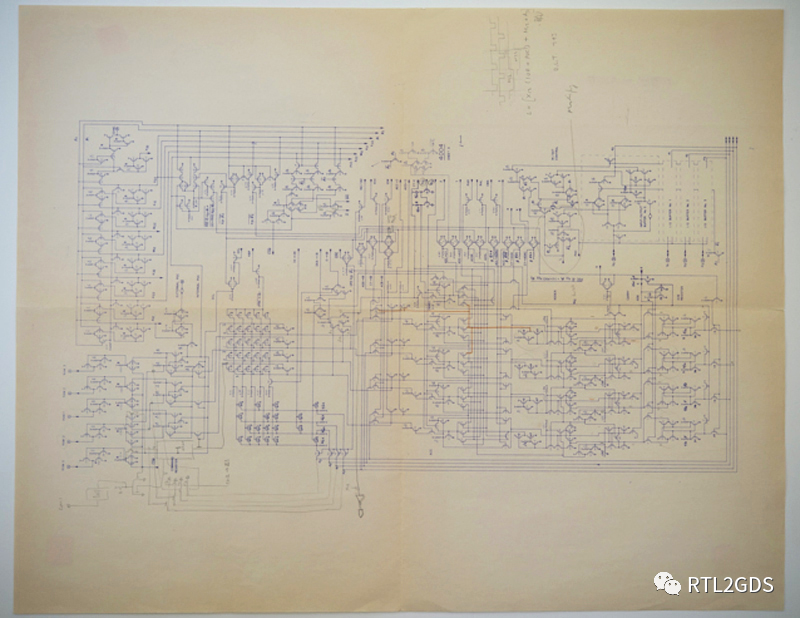

下图是范金的电路图手稿,用铅笔绘制在3张图纸上。第一张是Memory模块的电路图,第二张是控制逻辑模块的电路图,第三张是运算处理模块的电路图,可以实现加、减、移位等操作。

在电路设计上,范金有很多创新,例如静态MOS管移位寄存器,新型计数器,以及自动上电复位电路等等,都有专利可查。

Memory模块的电路图

控制逻辑模块的电路图

运算处理模块的电路图

版图设计(PnR)

在范金来之前,Intel并没有针对微处理器设计的方法学,而且该项目进度已经落后6个月。但是,作为一个专业的工程师,范金有着活人不能被尿憋死的精神,随着项目的进展,他摸索出一套适用于类似于微处理器的随机逻辑门电路设计和实现的方法学。

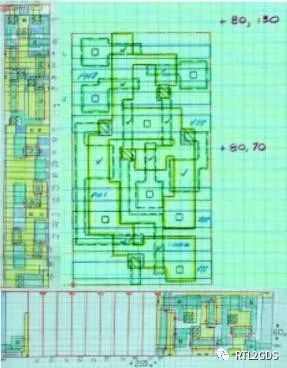

首先,当时没有DC和ICC2等EDA工具,逻辑设计和电路设计都是手工完成,需要同步考虑版图设计,标注逻辑门的物理信息,这样可以减少翻译过程中的错误,同时缩短总体开发周期。范金还设计了一些标准化单元,进行模块化设计,同时制定了简单的布局布线规则,根据这些规则,能够快速地基于负载大小计算出MOS管尺寸,与后来的NLDM的概念类似。

此外,版图设计是基于网格(Grid)的,所有的Poly和Metal都要分布在网格上,让看似杂乱的版图设计工作井然有序,大大降低了布局布线的难度,这套规则至今我们依然在沿用。下面就是一个标准逻辑门基于网格的版图设计实例,纯手工绘制,同样需要人工DRC检查,人工LVS检查。

标准逻辑单元的版图设计图纸

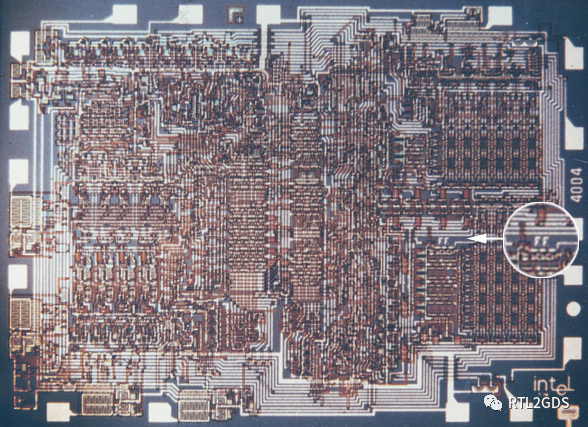

下图是整个4004芯片的Die 照片,其中还圈出了范金的签名(F.F.)。这种通过手工制作的方式很容易出错,比如Intel早期的一颗存储芯片就因为绘制中出错导致少了一个比特。

Intel 4004 Die 照片

总结

虽然现在Synopsys和Cadence的EDA无比强大,而且大公司的流程也非常完善,但是在新的工艺和新的设计出现时,新的问题还是会需要人工去寻找Workaround,推动EDA不断发展的正式这些探索者们。范金在半导体的石器时代,不断地锐意进取,为当今的信息和智能时代添砖加瓦,值得我们尊敬。