导读:通常来说,晶体管与导电金属的触点是由一个多层工艺形成的。

周一,美国半导体设备供应商应用材料公司(Applied Materials)推出一项构建晶体管和其他金属导线连接的新工艺技术,能够用于提升晶体管连接区域的导电性,进而突破芯片的运算速度瓶颈。

利用应用材料公司的新技术,晶体管及其连接区域的制造节点可以推进到5nm、3nm及以下,芯片的功效、性能、面积/成本(PPAC)能够同步提高。

一、传统晶体管连接方式阻碍晶体管尺寸缩小

计算机芯片由晶体管组成。晶体管可以被视为一种“开关”,能帮助计算机芯片实现1和0的数字逻辑。但是,只有在与导电金属连接时,这些晶体管才能发送和接收信号。

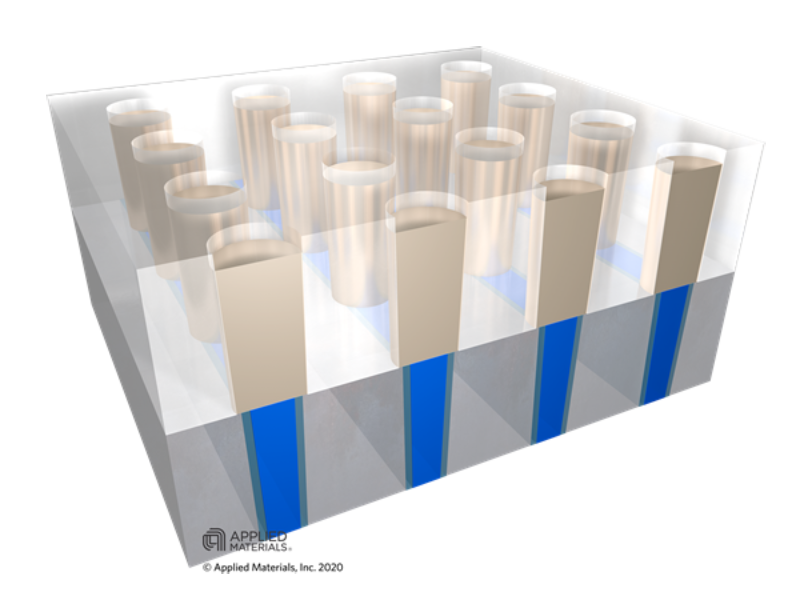

通常来说,晶体管与导电金属的触点是由一个多层工艺形成的。芯片制造商首先在触点通道内衬一层氮化钛制成的黏着层和阻挡层;然后,在触点通道内沉积一层成核层;最后,用导电金属钨填充剩余的空间。

在这几种材料中,钨的电阻较小,能让电子快速通过,相较于其他材料,更有助于加速芯片运算。

在7nm制造节点,晶体管与导电金属的接触通孔直径只有约20nm,liner-barrier和成核层占据了其中75%的空间,钨金属只能占据剩余25%的空间。细钨丝的接触电阻很高,这阻碍了面积/成本的提升和进一步实现2D微缩。

应用材料公司半导体产品部门副总裁Kevin Moraes称:“过去几十年间,业界依靠2D微缩来提升(芯片的)功效和面积/成本。但是今天,(芯片的)几何结构变得如此之小,以至于我们正在逼近传统材料和材料工程技术的极限。”

半导体行业市场研究公司VLSI Research董事长兼首席执行官Dan Hutcheson表达了相似的看法,他认为随着EUV到来,我们需要解决一些关键的材料工程挑战来延续2D微缩的发展,“在我们行业,liner-barrier等同于医学中的动脉斑块,使芯片失去了达到最佳性能所需的电子流。应用材料公司的选择性钨沉积是我们一直在等待的突破。”

二、应用材料新技术:选择性沉积低电阻的钨金属

Dan Hutcheson所提到的选择性钨沉积,即是应用材料公司最新研发的选择性钨化学气相沉积(ENDURA VOLTA SELECTIVE W CVD)系统,可以克服传统晶体管连接方式的局限性。

利用这个系统,芯片制造商可以在晶体管连接区域中选择性地只沉积电阻率较低的钨金属,不再需要liner-barrier和成核层,进而有助于提升计算机芯片的连接速度。

据了解,应用材料公司提出的选择性钨沉积系统是一个集成材料解决方案,在一个清洁、高真空的环境中结合多种工艺进行。晶圆采用原子级表面处理和独特的沉积工艺,使钨原子选择性地沉积在通孔中、形成完美的自下而上填充、没有分层、接缝和间隙。

应用材料公司称,作为其创新性选择性工艺技术产品组合的最新成员,全新Endura系统已成为多家全球领先客户的选择,目前,应用材料公司暂未透露这些客户的身份。