导读:设计自动化会议 (Design Automation Conference:DAC) 最近在旧金山举行。在演讲中,涵盖了广泛的领域——例如,设计自动化算法领先技术、商业 EDA 工具的新功能、技术和财务趋势和预测以及行业标准活动。

设计自动化会议 (Design Automation Conference:DAC) 最近在旧金山举行。在演讲中,涵盖了广泛的领域——例如,设计自动化算法领先技术、商业 EDA 工具的新功能、技术和财务趋势和预测以及行业标准活动。

近年来,DAC 组委会将传统算法/工具的重点扩展到新颖的 IP、SoC 和系统设计技术和方法。Design and IP Track 中的演讲深入探讨了团队如何解决新硅和封装技术带来的日益增加的复杂性,以及确保满足对可靠性、安全性和安全性的更严格要求。

下面附上一份来自笔者对 DAC 的印象盘点。其中提到,机器学习 (ML) 技术对芯片设计的性质和 EDA 工具本身的影响越来越大,这可能不足为奇。基于云计算资源的影响在趋势演示中也很普遍。

以下是笔者总结的10 大要点:

(10)系统公司和EDA要求

几场与趋势相关的演讲强调了超大规模数据中心和系统公司在内部加强SoC 设计团队方面的投资——例如谷歌、Meta、微软、亚马逊等。小组讨论会询问这些公司的代表——“你需要从 EDA获得什么?”。他们的回答可以用四个词来概括:“更大、更快的仿真系统”。

(顺便说一句,他们谈到了一个相当惊人的财务预测是,“所有 EDA 收入的 50% 最终将来自系统公司。”)

(9) 特定领域的架构

他们预期,无晶圆厂、IDM 和系统厂的IC 设计人员将越来越多地寻求通过将“特定领域架构”作为 SoC 和/或封装集成的一部分来使他们的产品与众不同。正如稍后将要讨论的,无论是追求数据中心训练还是数据中心/边缘推理,ML 机会对产品功能的影响都是 DSA 设计的关键驱动因素。

反对 DSA 设计的论点是 ML 网络拓扑继续快速发展(参见 (6))。对于数据中心应用,通用可编程引擎,例如具有丰富指令集架构的GPGPU/CPU,可以提供更大的灵活性以快速适应新的网络类型。一位主旨发言人提供了以下观点:“这是计算的能源成本与数据移动之间的权衡。如果通用 (GPU) 架构可以为复杂数据类型执行能耗密集型 MAC 计算,那么数据移动的相对成本就会降低,也意味着无需专门的硬件。”

(8) 多样化的设计开始

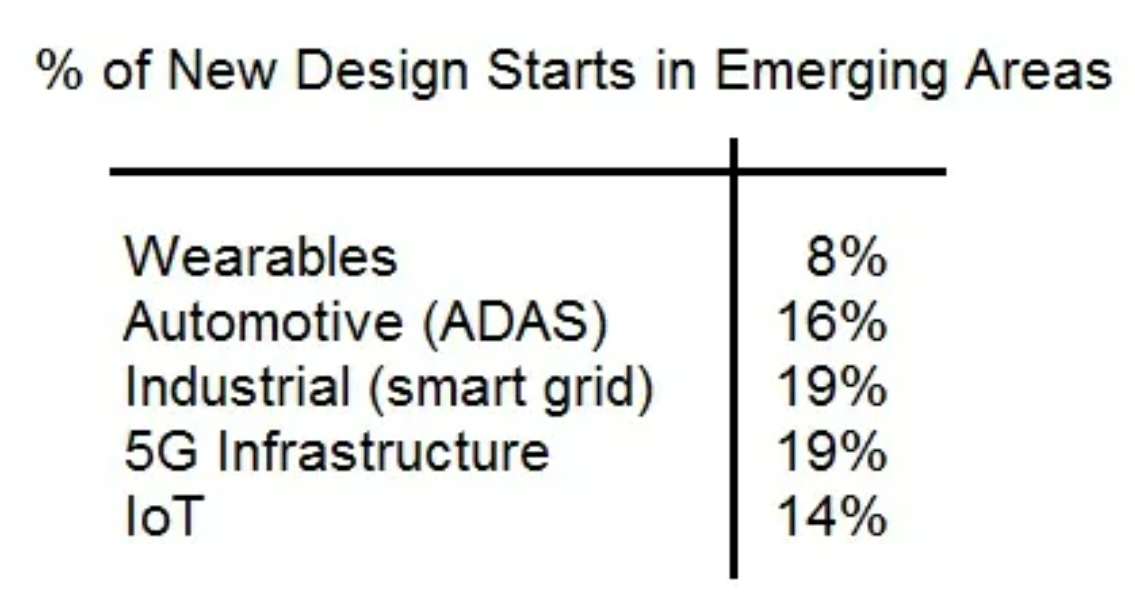

关于这部分,人们认为其驱动力的很大一部分来源是基于追求新 IC 设计的行业多样性。这种想法是,即使一个行业板块停滞不前,其他板块无疑也会有所回升。下图说明了新兴细分市场中设计起步的广度。

由于 EDA 行业增长严重依赖设计启动,因此他们的财务预测非常乐观。

(7) 过渡到云端

另一项预测——也许令人吃惊,也许并不令人吃惊——是“50% 的 EDA 计算周期将由云资源提供”。

演讲者的论点是,新的小型设计公司没有资源或兴趣构建内部 IT 基础设施,并且“对更新的方法和流程更加开放”。

一些 EDA 演示文稿承认需要解决这一趋势——“我们必须确保我们工具中的算法最大程度地利用多线程和并行计算方法,以支持基于云的计算。”

然而,并不是每个人都相信云过渡会顺利进行。

(6)“EDA许可需要采用SaaS模式”

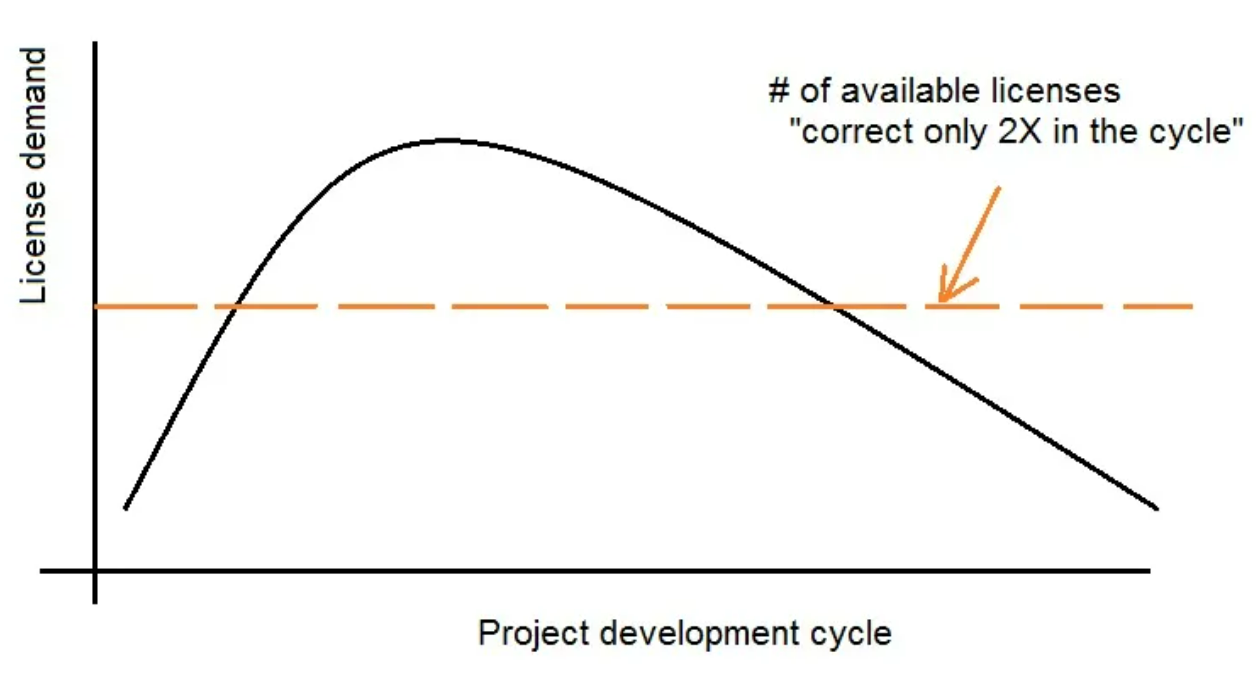

DAC 主题演讲者的一个非常尖锐的论点是 EDA 许可模式与利用云计算资源的趋势不一致。他认为,“EDA 许可证的数量在一个设计项目的整个时间表中只有两次是正确的(the amount of EDA licenses is right only twice in the overall schedule of a design project)。IT 行业的其他部门已经接受了软件即服务模型——EDA 公司也需要这样做。”

下图说明了“topped watch licensing model”。

在多年许可租赁协议中定期重新混合特定 EDA 产品的许可数量的机会在一定程度上缓解了这个问题。但主旨发言人承认,改变现有的许可财务模型会遇到来自 EDA 公司的相当大的阻力。

(5) 机器学习应用

在今年,有许多关于 ML 特定设计预期增长的演讲,包括非常高端的数据中心训练/推理和低端/边缘推理。

(a)高端数据中心ML增长

对于在超大规模数据中心运行的机器学习,重点仍然是提高图像和自然语言处理的分类准确性。一位主旨演讲者提醒听众:“虽然人工智能概念已经有几十年的历史,但我们仍然处于为这些应用探索机器学习架构的早期阶段。GPGPU 硬件对 ML 计算工作负载的适应实际上仅在 10 年前才开始。我们不断发展新的网络拓扑、计算算法和反向传播训练误差优化技术。”

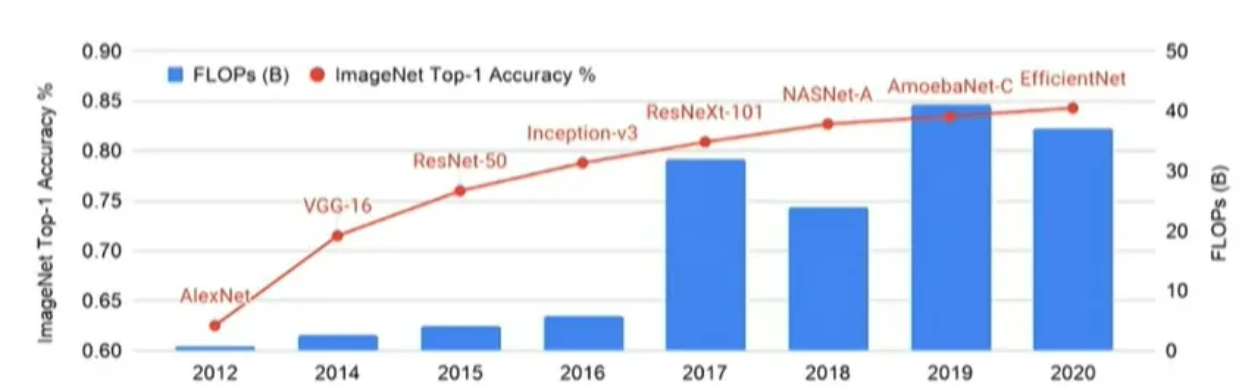

下图突出显示了过去十年用于图像分类的神经网络增长的复杂性,显示了提高分类精度所需的计算量。

(左轴是“Top 1”分类与标记训练数据集的匹配精度。继续关注提高准确性的一个迹象是,如果正确的标签在“Top 5”预测中,则神经网络曾经被赋予分类匹配的功劳)

(b)低边缘/边缘ML增长

相当多的技术和趋势演示侧重于使用于训练的 ML 网络适应边缘推理的严格 PPA 和成本要求。权重和中间网络节点结果的高精度数据类型可以量化为更小、更高效的 PPA 表示。

一位演讲者用以下场景挑战观众。

“考虑工业物联网 (IIoT) 应用,在这些应用中,传感器和传感器与低成本微控制器相集成,可提供实时监控。在许多情况下,仅仅检测超过某个阈值的振动、噪音或压力变化或图像缺陷是不够的——有必要将传感器输出分类为特定模式并做出相应响应。这非常适合使用在相应微控制器上运行的小型机器学习引擎。我敢打赌,观众中的许多人已经在考虑 IIoT ML 应用程序。”

(4) HLS与设计师生产力

有几场演讲鼓励设计团队采用更高级别的设计抽象和相应的高级综合,以解决日益增加的 SoC 复杂性。

鼓励设计人员访问SystemC.org,了解 SystemC 语言标准定义的最新进展,特别是 SystemC 可综合子集。

(3) 时钟

在设计团队面临的所有挑战中,从众多 DAC 演示中可以清楚地看出,管理当前 SoC 设计中越来越多的时钟域至关重要。

从架构的角度来看,设置和(完美地)执行时钟域交叉 ( clock domain crossing:CDC) 检查以确保正确同步至关重要。

从物理实现的角度来看,开发时钟单元布局和互连布线策略以实现延迟目标和观察偏斜约束(skew constraints)是非常困难的。一篇有见地的论文强调了 PCIe5 IP 宏的(多路复用)时钟管理和分配方面的挑战。

物理综合流程越来越多地利用时钟到达端点之间的“有用偏差”(useful skew)作为解决长路径延迟的另一种优化方法(并且作为间接好处,分配瞬时开关活动)。

一篇引人注目的 DAC 论文强调了偏移确实有助于关闭“late”时序,但可能会加剧“early”时序路径,需要更大的延迟缓冲来修复保持路径(hold paths)。作者描述了一种独特的方法来确定有用的偏斜实现(skew implementations)的组合,以调整延迟和早期时钟到达端点,以减少保持缓冲(hold buffering),节省功耗和块面积。

静态时序分析需要认真注意时钟定义和时序约束——在整个工作条件范围内进行多模式、多角(multi-corner )分析的努力成倍增加。一个演讲侧重于需要关注改进的方法来表征和分析具有统计变化的时序。在未来,告诉项目管理“设计接近于 n-sigma 时序”将变得更加普遍。

(2) EDA 中的机器学习

有很多演讲谈到了ML技术是如何影响EDA工具和流程。以下是一些观察:

(a)ML “inside”

一种方法是将机器学习技术直接整合到工具算法中。这是一个主题演讲中发人深省的评论:

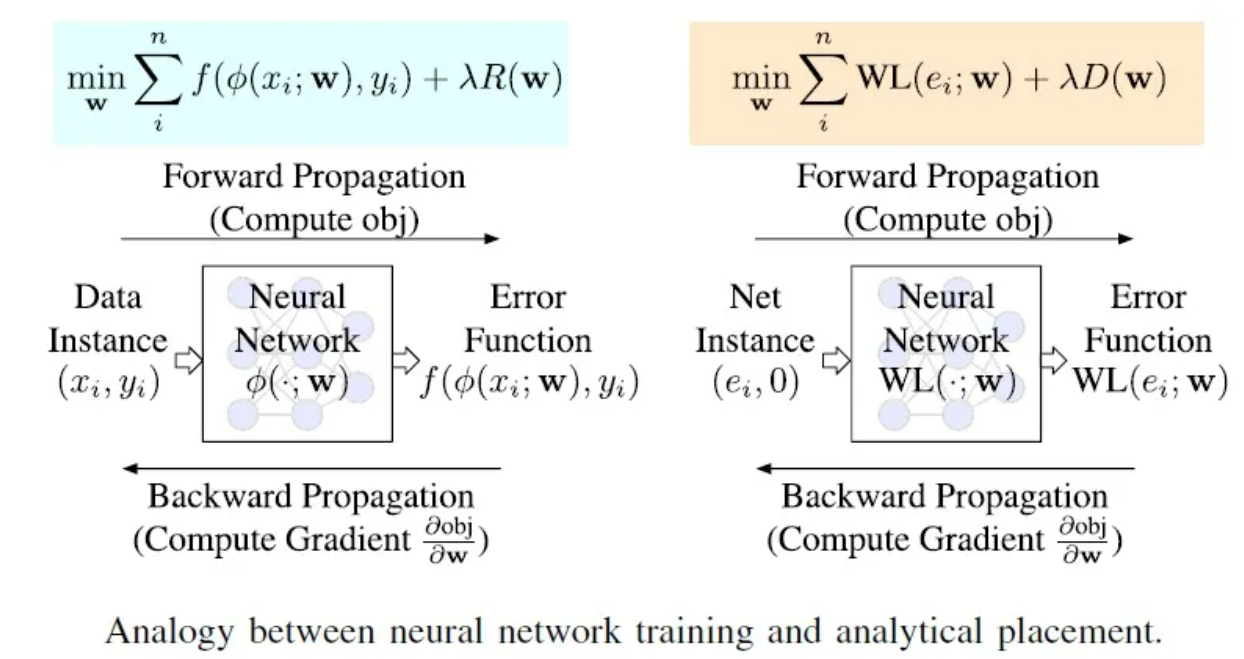

“ML 网络的训练需要一个输入状态,然后向前计算一个结果。有一个误差函数作为优化目标。该函数相对于现有网络参数的偏导数的反向传播推动了迭代训练的改进。EDA 中有类比——考虑单元格放置。”

主题演讲者继续说道:“当前布局用于计算由总网络长度估计、本地布线拥塞和关键网络时序组合而成的结果。目标是优化此(加权)结果计算。这是在单元放置优化算法中使用 ML 技术的理想应用。”

(b)ML “outside”

另一种方法论是在现有 EDA 工具/算法的“外部”应用 ML 技术。例如,块物理实现是一个迭代过程,从使用早期 RTL 的初始结果到随后的 RTL 模型发布。此外,物理工程师使用整个流程中提供的各种约束组合对单个模型进行迭代,以评估 QoR 差异。这种在开发周期中积累的物理数据可以作为 ML 训练的(特定于设计的)数据集,帮助工程师开发最佳流程。

(1) 功能安全与保障

可能对整个设计和 EDA 行业产生影响的最具挑战性、最具破坏性且最令人兴奋的领域是满足功能安全和安保要求的日益增长的需求。

虽然经常被一起提到,但功能安全和保障有很大不同,据一位 DAC 演示者称,“甚至可能相互冲突”。

FuSa(for short)是指为响应系统和/或随机故障而包含的必要硬件和软件设计功能。一位演讲者强调,基础设施已经到位,使设计人员能够通过 ISO 26262 和 IEC 61508 标准结构识别和跟踪FuSa 功能的定义和验证,他说:“我们知道如何通过流和供应链传播 FuSa 数据. 相应地,我们对软件工具的使用充满信心。”然而,同一小组的一名成员说:“现在的挑战是建立专业知识以了解在何处以及如何插入 FuSa 特征。您如何确保系统在遇到随机故障时能够正确运行?FuSa 作为一门工程学科,我们仍处于起步阶段。”

EDA 行业通过提供特定产品来协助 ISO 26262 数据依赖性管理和可追溯性,对 FuSA 开发日益重要的重要性做出了回应。

安全问题在整个行业中不断出现。简而言之,电子系统的安全性包括:

旁道攻击(例如,敌手监听发射)

恶意硬件(例如,制造流程中插入的“木马”)

逆向工程(攻击者访问设计数据)

供应链中断(例如,克隆、赝品、重新标记模块;期望芯片将被识别、验证和跟踪)

设计实现流程需要添加安全硬件 IP 以防止这些攻击“surfaces”。

对我而言,产品 FuSa 和安全要求的影响将对系统设计、IP 开发和 EDA 工具/流程产生普遍影响。