导读:本次,三星电子的研究团队通过构建新的 MRAM 阵列结构,用基于 28nm CMOS 工艺的 MRAM 阵列芯片运行了手写数字识别和人脸检测等 AI 算法,准确率分别为 98% 和 93%。

近日,三星电子在顶级学术期刊 Nature 上发表了全球首个基于 MRAM(磁性随机存储器)的存内计算研究。

存内计算由于无需数据在存储器和处理器间移动,大大降低了 AI 计算的功耗,被视作边缘 AI 计算的一项前沿研究。虽然 MRAM 存储器件具备耐用性、可大规模量产等优势,但其小电阻的特性阻碍了这类存储器被用于存内计算。

本次,三星电子的研究团队通过构建新的 MRAM 阵列结构,用基于 28nm CMOS 工艺的 MRAM 阵列芯片运行了手写数字识别和人脸检测等 AI 算法,准确率分别为 98% 和 93%。

研究扩展存内计算类型,填补 MRAM 空白

在传统的计算机架构中,数据需要从内存移动到处理单元,然后将中间结果存储回内存。但这种无谓的信息传输不仅增加了计算延迟,也提升了相关功耗。

根据台积电此前对存内计算的研究,数据移动所消耗的能量甚至大于计算的能量消耗。因此,在内存中同时执行数据存储和计算的存内计算成为了行业与学术机构研究的焦点。

此前的研究中,非易失性的 RRAM(电阻式随机存取存储器)和 PRAM(相变随机存取存储器)是存内计算最常用的两类存储器。相比之下,尽管 MRAM 器件在操作速度、耐用性和量产等方面具有优势,但其较低的电阻使 MRAM 存储器在传统的存内计算架构中无法达到低功耗要求。

在本篇论文中,三星电子的研究人员构建了一种基于 MRAM 的新存内计算架构,填补了这种空白。论文特别写道,该研究并非和基于其他存储器的存内计算架构竞争。到目前为止,没有一种存储器类型在电子产品中占据绝对主导,因为不同类型的存储器各有自身的优点和缺点。因此,基于不同存储器的存内计算也可能发展成不同的架构。

从这个角度看,三星电子通过填补基于 MRAM 存储器的存内计算架构空白,有助于存内计算发展。

▲ 三星研究团队:共同通讯作者 SAIT(三星高级技术研究所)院士、哈佛大学教授 Donhee Ham(左一);论文一作 SAIT 研究员 Seungchul Jung(左二);共同通讯作者 SAIT 技术副总裁 Sang Joon Kim(左三)

基于 28nm CMOS 工艺,准确检测 1851 张人脸

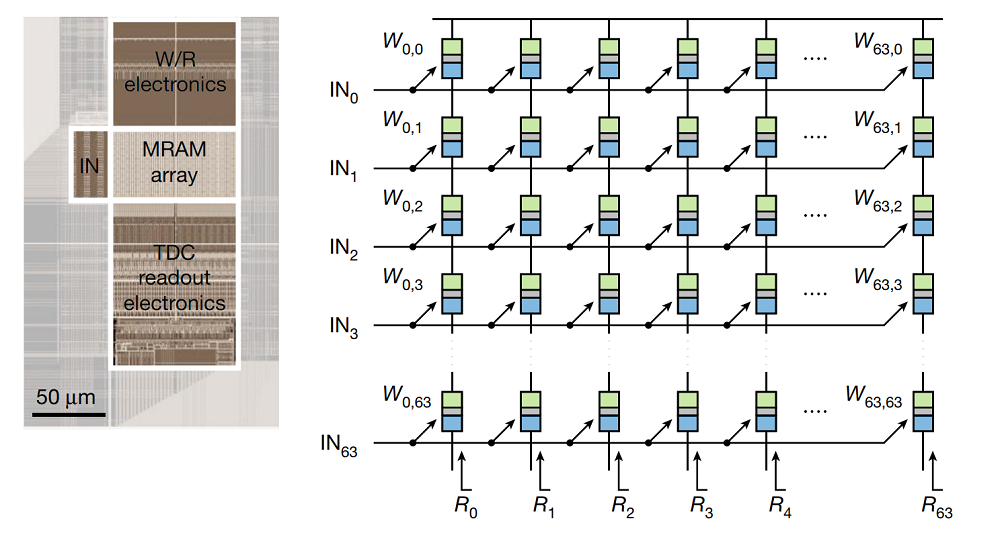

三星电子构建了一个 64×64 的 MRAM 阵列,其外围电路通过 28nm CMOS 工艺进行了集成。

具体结构上来说,MRAM 阵列在写 / 读(W / R)电子元件和底部的 TDC 读出电子元件之间,输入数据控制器(IN)位于阵列左侧。

为了弥补 MRAM 小电阻的问题,三星电子引入了一种新的位单元(阵列行列交叉处的元素,bit-cell),每个位单元组合成两条路径,每条路径则由一个 MTJ(磁性隧道结)和一个 FET(场效应管)开关串联组成。

▲ 芯片布局与 MRAM 阵列排布(图片来源:Nature)

研究人员将每列中这些新的位单元串联起来,每个位单元的输出电阻相加便得到了列电阻 R。通过新的结构设计,列电阻 R 取代了传统(存内计算)结构中基于基尔霍夫定律的列电流总和,成为了列输出,解决了 MRAM 器件电阻较小的问题。

简单来说,就是三星电子开发了一种 MRAM 阵列芯片,用新的“电阻总和”内存计算架构取代了标准的“电流和”内存计算架构,从而解决了单个 MRAM 器件的小电阻问题。

为了将这种新的 MRAM 阵列用于 AI 计算,研究人员采用了二值神经网络(BNN)算法。这种算法的精度可以以网络大小为代价,将每个实值权值表示为二值化函数,或以计算速度为代价将每个实值输入数据表示为多个二值化函数序列,以提高 BNN 算法的精度。

该研究中,三星电子采用了后一种方式,将每个输入数据扩展为 8 位编码,以抑制噪声。之后,研究人员用两层 BNN 网络以对 MNIST 数据集进行分类。

MNIST 数据集来自美国国家标准与技术研究所(NIST),训练集和测试集均由不同的手写数字组成,数据集和测试集 50% 的手写数字来自高中生,另外 50% 来自美国人口普查局的工作人员。

▲ 不同的手写数字 7(图片来源:CSDN)

研究人员用 MRAM 阵列执行了对 1 万个手写数字图像的分类,并重复了三次,得到了 93.23±0.05% 的准确率。测试后,研究人员又通过 VGG-8 神经网络对 1 万个手写数字图像进行了分类,其准确率高达 98.86±0.06%。

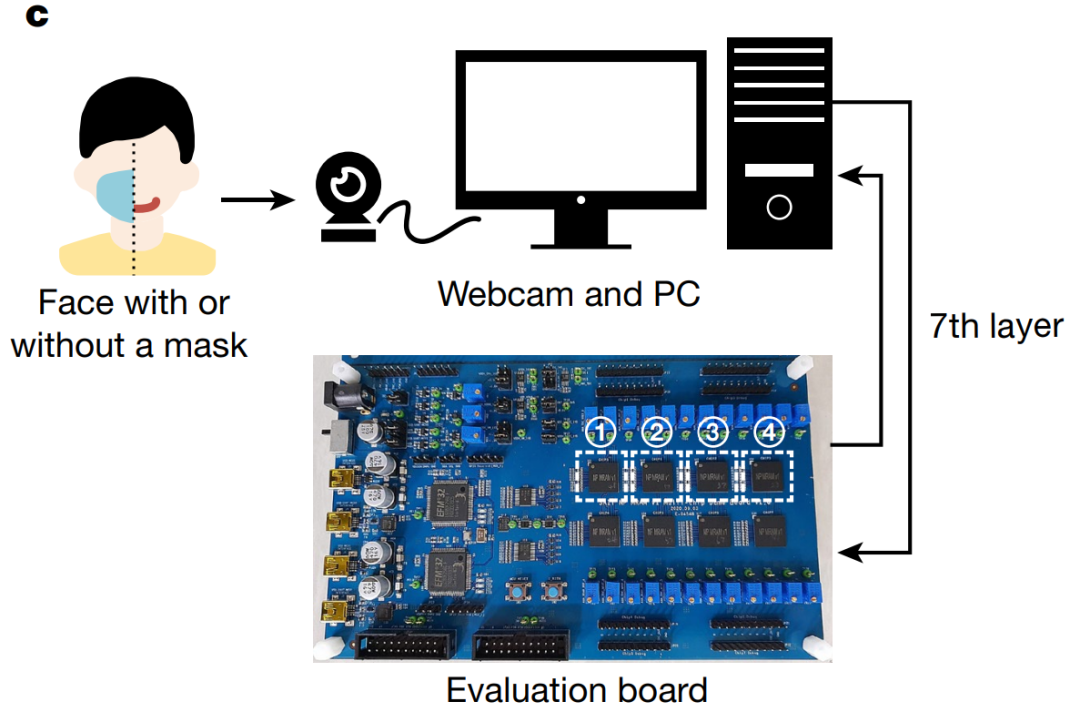

除了手写数字分类,三星电子还用 4 个 MRAM 阵列芯片运行了人脸检测算法。在这一步,MRAM 阵列芯片并没有对场景中的所有对象进行人脸认证,而是先检测场景中是否存在人脸,确认存在后再激活更高功率的人脸认证算法。

通过这种方法,MRAM 阵列芯片从 2000 个无遮罩人脸场景中检测到 1851 张人脸,准确率为 92.5%;从 500 个遮罩人脸场景中检测到 483 张人脸,准确率为 96.6%,总体准确率为 93.4%。此外,MRAM 阵列芯片可以和相机结合实时检测人脸。

▲ 4 个 MRAM 阵列芯片与相机相连实时人脸检测(图片来源:Nature)

集成多种器件面临挑战,未来或可用于生物神经元网络

对于这项研究,研究人员写道,MRAM 阵列运行存内计算的一个重要挑战是构建 AI SoC(片上系统),将许多阵列和数据转换器、数字电子设备进行集成。

研究人员还强调,宽泛来说,内存阵列不仅可以用来运算神经网络算法,也可以作为潜在的生物神经元网络载体。

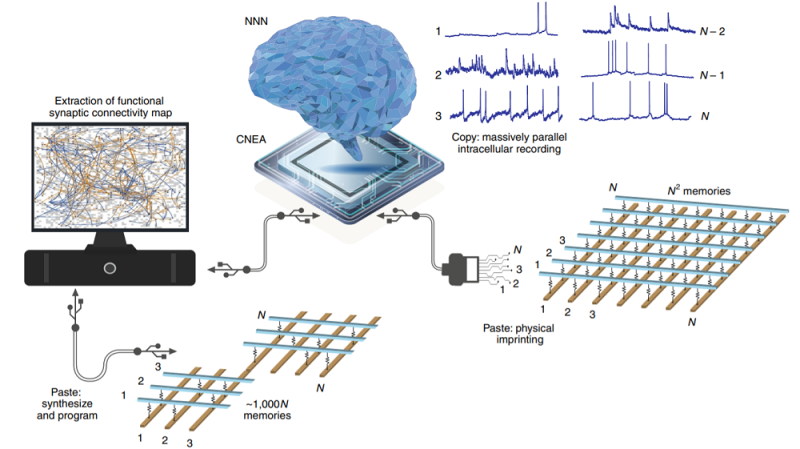

2021 年 9 月,三星电子和哈佛联合在 Nature 子刊 Nature Electronics 上发表了名为《Neuromorphic electronics based on copying and pasting the brain(基于复制和粘贴大脑的神经形态电子学)》的论文,提出了一种将大脑神经元连接图(neuronal wiring map)“复制、粘贴”到高密度 3 维存储网络上的可能。

▲ 三星此前“复制、粘贴”大脑的研究(图片来源:Nature)

MRAM 阵列研究的第一作者 Seungchul Jung 称,存内计算与人类大脑的计算类似,因为人类的计算也发生在记忆或突触网络中。虽然 MRAM 阵列当前的计算目的并非模仿大脑,但这种固态存储网络将来可能会被用作模拟大脑突触的平台。

结语:新研究或将丰富三星存内计算产品

近年来,存内计算已逐渐成为产业界和学术界的公识,相关论文反复出现在 ISSCC 和 IEDM 等电子领域的顶级会议中,台积电等半导体头部厂商也都在布局和探索。

三星电子作为全球存储龙头,更是一直在关注存内计算技术。去年 2 月,三星电子便公布了其首款集成了 AI 计算能力的高带宽内存(HBM),可以节省 70% 以上的能耗并提供 2 倍以上的系统性能。本次基于 MRAM 的存内计算研究丰富了三星在存内计算领域的布局,未来或许能够看到更多类型的存内计算产品出现在市场上。