导读:在semiengineering的这个采访中,Siemens Digital Industries Software的 MPC 和掩模缺陷管理总监 Peter Buck ;Hoya 技术战略高级总监 Bryan Kasprowicz;和D2S的首席执行官 Aki Fujimura就光罩的相关问题进行了讨论。

因为高性能芯片的需求,芯片制造工艺一直已经在摩尔定律的指导下,推到了3纳米,随之而来的是各种制造挑战。在semiengineering的这个采访中,Siemens Digital Industries Software的 MPC 和掩模缺陷管理总监 Peter Buck ;Hoya 技术战略高级总监 Bryan Kasprowicz;和D2S的首席执行官 Aki Fujimura就光罩的相关问题进行了讨论。

SE:我们真的需要扩展节点并开发 3nm 及以上技术吗?摩尔定律正在终结,还是正在放缓?

Fujimura:是的,至少在半导体市场的高性能计算细分市场中,我们肯定需要每瓦特和每美元更多的计算量。智能家居产品和其他物联网设备更喜欢更低的成本而不是更高的性能。但天气预报、比特币挖掘或深度学习等重度模拟正在推动对 3nm 及以上技术的需求。幸运的是,我们将继续扩大规模,尽管摩尔定律正在发生变化。该行业跨学科和竞争对手之间的协作能力至关重要。这样,行业才能继续取得进步。这是一件好事,因为我们在 D2S 所做的一切都取决于它。我们热切期待下一代 GPU、CPU、内存、通信芯片等,所有这些都将继续按照摩尔定律扩展。对于极紫外 (EUV) 光刻时代的逆光刻技术 (ILT:inverse lithography technology ),多年来我们需要更强大的机器来提供更优质的晶圆。即使是现在,我们也可以使用 10 倍以上的计算能力。由于我们需要我们的技术来针对越来越小的几何形状,因此计算需求在此基础上不断扩大。毫无疑问。我们需要更多的计算能力。

SE:2018 年,三星和台积电为 7nm 工艺节点带来了 EUV 光刻技术。现在,使用 EUV,芯片制造商正在生产 5nm 的芯片。尽管如此,我们仍然在这里听到有关mask 3D的消息。那是怎么回事?

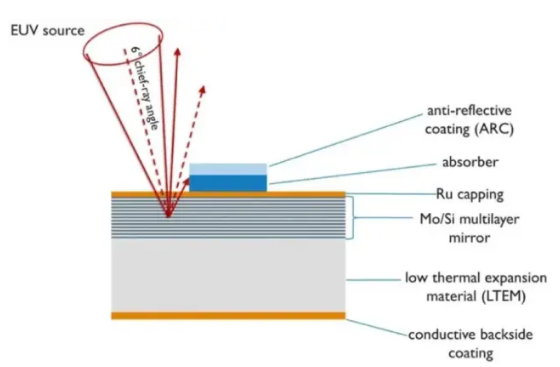

Kasprowicz:在 EUV 中,您有反射光学元件。如果你将光垂直于镜子曝光,它会直接回到 EUV 扫描仪的光学柱中,并且不会击中晶圆。例如,当您照镜子时,您看到的是自己的倒影。如果您在反射式光学元件下的 EUV 扫描仪内执行此操作,也会发生同样的事情。所以在 EUV 中,光线必须以一定角度照射到掩模上。因为你有一个角度,所以 EUV 掩模和吸收器(absorber)的深度和高度很重要。在某些时候,光罩上的吸收器可能会变得太高。在这种情况下,它不仅仅是“X”和“Y”,而是现在您正在查看它的“Z”组件。因此,当您为其添加深度时,您会开始获得一些所谓的阴影效果。如果这不是问题,我们可能会在 EUV 掩模上使用更厚的吸收器,即使在 7nm 或人们开始实施 EUV 光刻的时候。因此,我们试图使吸收器尽可能薄,以减轻这些mask 3D 效果。因此,您使用的吸收器越薄,您对这些 3D 效果(例如shadowing, telecentricity和pitch walking等)的影响就越小。但这也有很多其他的含义。具体来说,当您尝试使用较小的功能进行 OPC(光学邻近校正)时,这些效果确实会产生影响。随着音高的收紧,这些情况会变得更糟。但这也有很多其他的含义。具体来说,当您尝试使用较小的功能进行 OPC(光学邻近校正)时,这确实会产生影响。

图 1:EUV 掩模的横截面。EUV 光以一定角度照射掩模,产生阴影或mask 3D 影响。

SE:今天,芯片制造商正在研发 3nm 工艺。最初,在 3nm,芯片制造商将继续使用现有的具有 0.33 数值孔径 (NA) 的 EUV 光刻扫描仪。这对 3nm 的 EUV 掩模意味着什么?mask 3D 影响怎么样?

Hayashi:我们将在这里继续使用 0.33 NA EUV。那时,高数值孔径的 EUV 还没有准备好使用。基本上,客户将使用 0.33 NA 的 EUV 双图案。因此,在这种情况下,掩模分辨率并不是那么具有挑战性。但客户希望提高对比度和图案保真度。有了这些要求,我们应该选择更薄的薄膜或吸收体来减少 3D 效果。我们还应该考虑使用相移材料来提高对比度和吞吐量。此时,掩膜类型取决于应用层。例如,相移掩模非常适合接触孔类型的应用。在这一领域,掩膜制造和掩膜材料在生产技术以及新材料方面都面临着一些挑战。

SE:今天,在研发方面,该行业正在开发一种称为High NA EUV 的下一代 EUV 光刻技术,计划于 2024/2025 年推出。高数值孔径 EUV 对光掩模行业意味着什么?

Fujimura:High-NA EUV 是下一代 EUV 光刻技术,可将数值孔径 (NA) 增加到 0.55。由于可写分辨率是波长除以 NA,因此较大的 NA 可以跨制造变化准确地写入较小的特征。实现此目的的方法之一是使用变形 4X:8X 掩膜。传统的掩膜是 4X:4X 放大倍率。无论如何,用于High NA EUV 的掩模暴露了晶圆上一半的场大小。用于High NA 的掩模与传统掩模的物理尺寸相同,以保持掩模基础设施相同。这样一来,您就可以在掩模商店的同一条生产线上生产传统掩模和High NA 掩模。

Kasprowicz:目前的想法是,我们应该能够在早期使用和利用为先进的 0.33 NA EUV 开发的现有空白材料。正在开发的现有先进二元或相移掩模应该能够简单地转换为High NA EUV 的起点。集成用于High NA 的掩模解决方案不应进行大量初始开发工作。

随着我们可能再增加一个节点,我们将不得不开始寻找一种替代的多层 EUV blank,以提高telecentricity,减少光线进入镜面的穿透深度。也许那时也有不同的上限结构。如果需要新的多层,二元 EUV 掩模结构也可能随时间改变。随着我们开始缩小特征尺寸,相移 EUV 掩模可能会发生变化,原因与 0.33 NA 相同。我们可以在那里实施不同的标线增强技术 (RET:reticle enhancement technology ) 结构。在大多数情况下,为先进的 0.33 NA EUV 掩模开发的许多元素应该对High NA 早期阶段的很大一部分有用。也许几年后,我们将不得不考虑对blank进行一些更改。目前仍在讨论有关过渡时间的问题。当然,就blank本身而言,事情会变得更加紧张。平整度规格将变得更加严格。粗糙度规格将变得更加严格。然后,您会得到诸如波长在多层反射镜反射率上的扩散之类的东西。这些事情将不得不变得更加严格。

Hayashi:我们正致力于开发用于二元 EUV 掩模和High NA EUV 相移掩模的新材料。这些材料非常不寻常。例如,对于二元掩模,我们必须为吸收体选择High k 材料。目前,用于 EUV 掩模的吸收器是基于钽材料的。对于下一代二元掩模,我们正在研究镍等其他材料。然后,相移掩模将需low n材料,包括钌或铂。这些材料基本上很难蚀刻。因此,掩膜生产技术面临一些重大挑战。我们也可能需要一种新的掩模制造光刻胶。EUV 光刻也是如此。对于掩模,我们需要更高的分辨率,即使在 4X 掩模上也可能小于 20nm。我们需要一种非常薄的高分辨率掩模光刻胶。它不会是当前材料。也许我们必须使用金属氧化物类型的材料,就像许多人在 EUV 光刻中寻找的那样。因此,掩模制造面临着几个材料和工艺挑战。

Buck:掩模写入器将面临持续的压力,要求他们在不失去现有吞吐量优势的情况下提高分辨率。现在,我们看到了 30nm 的最小特征尺寸。如果它们要达到 20nm 左右,则需要改进整个掩模成像基础设施,例如抗蚀剂、掩模写入器和 MPC(掩模工艺校正),以满足这些要求。

Hayashi:我对高数值孔径 EUV 的变形光学很好奇。使用该镜头,High NA 使用 4X 和 8X 放大倍率。也许它不会对掩膜制造产生太大影响。但如何衡量或保证掩膜质量是这里的挑战之一。例如,如何测量斜线宽度,它的角度会与设计的不同。具有变形光学元件的 EUV 航空图像显微镜将有助于更轻松地评估晶圆上的图像,包括缺陷可印刷性以及不同的放大轴。

Kasprowicz: 高数值孔径的扫描仪肯定有更好的分辨率。但是缺陷尺寸要求和缺陷规格变得很小。从掩模blank的角度来看,您需要更好的光学器件来进行光化掩模blank检测。波长不会改变,但您需要更好的光学器件,并且您可能需要更好的载物台来实现定位精度。到目前为止,对于 EUV 掩模来说,实现零缺陷是相当困难的。如果您找到它们,数量有限仍然可以。您只需能够使用 EUV 掩模本身上的基准标记或对齐标记来引用它们。然后,您发送该信息。这就是毛坯检测工具的阶段精度发挥作用的地方。一旦发现缺陷,您必须在合理范围内,以便客户在执行缺陷缓解计划时可以找到它们。然后在图案检查方面,有一些挑战。关于变形镜头的影响存在一些不确定性。当您查看变形宽银幕并且有缺陷时,由于放大倍率的差异,您在一个方向上可能比在另一个方向上更宽容。我期望必须做一些广泛的工作才能真正理解这一点。可能在blank或图案检查期间执行原位 AIMS 检查。当然,了解如何在掩模生产的后期图案阶段对这些缺陷进行表征和分类将是关键。当我们谈到相移时,它变得更加困难,在那里你有一些与之相关的传输和相位。这将与二进制不同,因此需要理解。

Buck:变形成像有许多挑战。例如,当您在 OPC 和掩模制作之间进行变形缩放时,45° 角会变成倾斜边缘。曲线结构的变形缩放甚至更加复杂。掩码线性签名的效果在“X”和“Y”中是不同的。可能存在与轴相关的掩模精度、线性度和最小特征尺寸规格。关键特征可能会有一个首选轴,这会在一定程度上影响设计方法。如果将 AIMS 用于缺陷可印刷性验证,则需要变形 AIMS 工具,这会增加生产变形掩模的成本。在变形 EUV AIMS 工具可用之前,缺陷可印刷性模拟可能在这里起到临时解决方案的作用。