导读:Chiplet“小芯片”在2019年小火过一把,当时Chiplet在AI芯片领域可谓热词,但在更早之前这个概念就已经出现了。

Chiplet“小芯片”在2019年小火过一把,当时Chiplet在AI芯片领域可谓热词,但在更早之前这个概念就已经出现了。Chiplet是硅片级别的重用,是一类满足特定功能的die,通过搭积木造芯片的模式,利用die-to-die内部互联技术将多个模块芯片与底层基础芯片封装在一起,构成多功能的异构System in Packages(SiPs)芯片的模式,建立一个Chiplet的芯片网络。

这也被认为是能延续摩尔定律“已死”的重要方案。

2019年AMD提出打破摩尔定律的限制,革命性的the Infinity Fabric(两个4核CPU互联的专门的通道)掀起了小芯片风潮。那时候对于这项技术的限制大部分都会提到互联标准和封装技术。

在3月2日,ASE、AMD、ARM、Google云、Intel、Meta(Facebook)、微软、高通、三星、台积电十大行业巨头联合宣布,成立行业联盟,共同打造小芯片互连标准、推进开放生态,并制定了标准规范“UCIe”。

UCIe标准的全称为“Universal Chiplet Interconnect Express”(通用小芯片互连通道),在芯片封装层面确立互联互通的统一标准,可在?芯?之间提供?带宽、低延迟、节能且具有成本效益的封装连接。

UCIe 1.0标准定义了芯片间I/O物理层、芯片间协议、软件堆栈等,并利用了PCIe、CXL两种成熟的高速互连标准。这个标准最初是由Intel提出并制定,后开放给业界,共同制定而成。

它解决了对计算、内存、存储和跨越云、边缘、企业、5G、汽?、?性能计算和?持领域的整个计算连续体的连接。UCIe 提供了封装来自不同来源的芯?的能力,包括不同的晶圆厂,不同的设计和不同的封装技术。这一波直接冲击的是芯片半导体行业,但其覆盖的垂直领域市场也是不可计量的。

为何是Chiplet封装集成?

我们先来区分一下SOC、SIP和Chiplet。

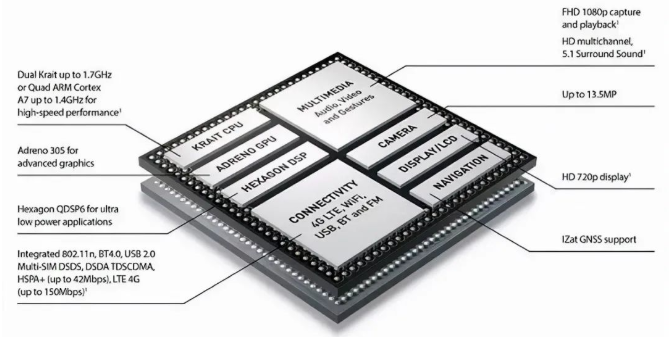

SOC(system on chip)片上系统。它是信息系统核心的芯片集成,是将系统关键部件集成在一块芯片上,像一个微小型系统。在PC时代我们可以说一个电脑的核心是CPU,而在智能终端时代,手机的核心就是SOC。它依然是遵循摩尔定律发展方向的。

SOC模拟示意图,图源网络

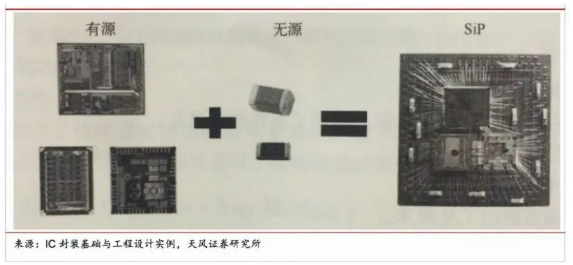

SIP(System-in Package)系统级封装。SIP封装并无一定型态,利用单纯的打线结合或覆晶接合,将处理器、存储器、FPGA等功能芯片以2D或者3D封装结构集成在一个封装内,可做定制化生产。SIP超越了摩尔定律的发展方向,在SIP中集成度较高的是蓝牙和802.11(b/g/a),多用于涵盖通信技术的解决方案,同时UWB是SIP的另一个理想应用。

Chiplet即芯粒,也称小芯片。它其实就是多个芯粒通过先进的封装技术形成的SIP,将不同工艺节点和不同材质的芯片通过先进的集成技术(如3D集成技术)封装集成在一起,形成一个系统芯片,实现了一种新形式的IP复用。它摆脱了摩尔定律的发展方向。

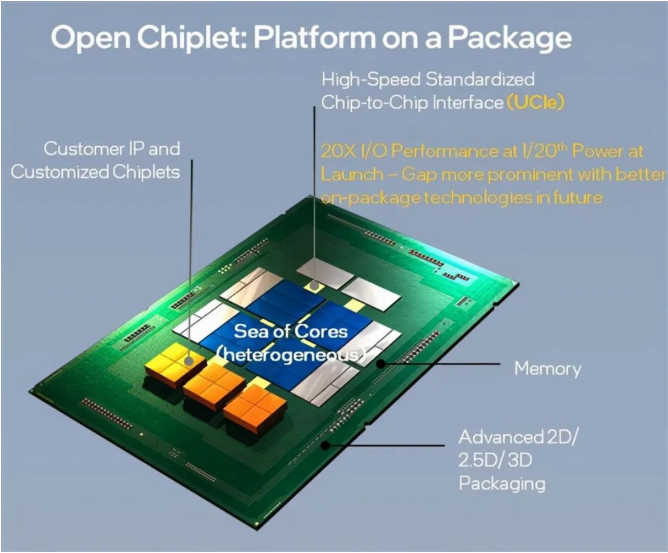

UCIe ?持在封装上交付平台的开放式 Chiplet ?态系统

发展了50多年的摩尔定律已然快到极限,现在行业的需求对于传统单一工艺、单一芯片的做法来说,难度和成本都越来越高,亟需变革。?芯?的封装集成能够以快速且经济?效的?式提供定制解决?案,例如,不同的?途可能需要不同的加速能力,但具有相同的内核、内存和 I/O。现在,它还允许根据功能进行最佳工艺节点选择的芯?共同封装,通过UCIe实现小芯片之间的封装互连,可以大大降低制造成本。

数据显示,10nm芯片的设计成本为1.744亿美元,7nm芯片飙升到2.978亿美元,5nm芯片更是高达5.422亿美元,即便是行业巨头也越来越吃力。而新的UCIe标准规范,让不同厂商的小芯片互通成为可能,x86、ARM、RISC-V集成在一起也有了实现之地。

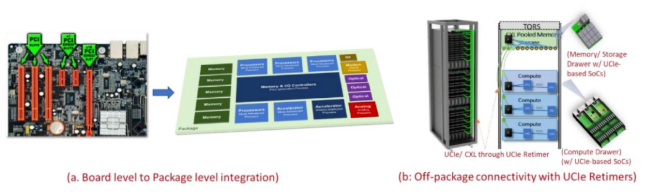

UCIe 1.0 定义了两种类型的封装:物理层和通信协议。?先是封装级集成,连接在板级的组件,如内存、加速器、网络设备、调制解调器等,可以在封装级集成,适?于从?持到?端服务器,通过不同的封装选项连接来?多个来源的芯?。其次是使?不同类型的介质(例如光缆、电缆、毫?波)提供封装外连接重定时器,?于在机架甚? pod 级别传输底层协议),以实现资源池、资源共享,在边缘和数据中?提供更好的能效和成本效益性能。

为什么物联网时代需要Chiplet

物联网最大的困境是碎片严重,包括技术碎片化,应用碎片化。

不同的应用场景需要不同的物联网技术能力,比如通信技术常见的有4G、5G、NB-IoT、Cat.1、LoRa、wifi、蓝牙、zigbee以及其他私有协议等等。

在某些场景中需要用到4G+蓝牙,某些场景需要用Cat.1+wifi或者Cat.1+wifi+蓝牙等各类差异化的需求。

当然,除了通信芯片,在IoT设备还有更多常用的IC器件,比如不同类型的MCU、电容、电感、内存、PA、还有数亿千计的传感器类别等等。

碎片化的IoT市场,注定不是一个通用IC就能用的,因为一个性能强大的IC当然也能覆盖很多应用场景,就好比用5G SoC去用于智能水表,当然也能用,但这属于“杀鸡用牛刀”,不仅浪费了5G的多数能力,也很贵,不是一种市场化的行为。

市场上对于技术方案的选择最终都会落实到性价比,而极度碎片化的IoT应用市场上需要根据需求才能定制出相应的最具性价比方案。

通用的方案行不通,而Chiplet提供的思路就是将不同功能的小芯片集成到一起,让芯片的能力可以像堆积木一样,堆积出自己想要的功能,这成了行业的必然之选。

广阔未来

随着垂直领域智能化需求的持续增加,图形处理、安全引擎、人工智能(AI)整合、低功耗物联网控制器等各种异构应用处理器需求的提升,市场研究机构Omdia曾预估2035年全球Chiplet可服务市场规模将一步提高至570亿美元。UCle标准的开放将会大大提高这个数值,在通信、工业等领域发挥更大的价值。

首先是架构设计的灵活性,硅片的互联让带宽,延时和功耗都会有巨大的改善。其次是商业模式的多样性,由于多模块的集合,拓宽了供应链和垂直领域的选择,可以挖掘到更多的潜在市场。

但Chiplet依然存在不少挑战,基于目前的国际形势和国内产业的实际发展水平,国内要面临的困难和国际头部IC设计公司并不相同。国内厂商也已经在推进Chiplet技术,像华为海思、中兴等已实现了一定的量产,但代工还是由台积电这些企业来完成。国内厂商要走“自研”路线,仍需打磨很长时间。

UCIe标准面向全行业开放,在物联传媒公众号对话框回复关键字“小芯片”即可下载相关白皮书。

参考资料:

快科技:AMD、ARM、Intel、高通、三星、台积电等十巨头在一起!打造小芯片互通规范

IC的帆哥:IP,SoC,SiP和Chiplet的区别

半导体行业观察:“延续”摩尔定律的Chiplet,应该走怎样的发展路线?