导读:“摩尔定律”曾主宰着半导体芯片一次次创造技术发展的奇迹,但近年来关于“摩尔定律”放缓甚至终结的声音愈演愈烈,“后摩尔时代”成为行业一大热词。

“摩尔定律”曾主宰着半导体芯片一次次创造技术发展的奇迹,但近年来关于“摩尔定律”放缓甚至终结的声音愈演愈烈,“后摩尔时代”成为行业一大热词。

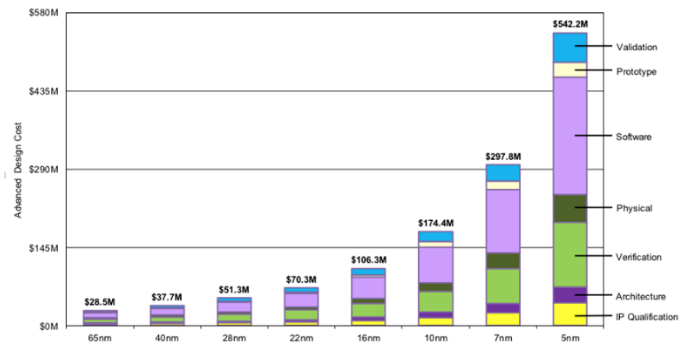

新工艺制程发展让芯片体积性能不断迭代,同时带来了高昂的科研成本:据IBS统计,一个28nm芯片的设计成本在4000万美元,16nm芯片设计成本约1亿美元,而5nm芯片的设计成本更高达5.4亿美元。工艺微缩的前景几乎打破摩尔定律 “投资发展制程——芯片生产成本降低——制程再投资”的逻辑。

来源:International Business Strategies (IBS)

在延伸“摩尔定律”的道路上,Chiplet(芯粒)生逢其时。

3月2日,英特尔联合10家芯片巨头成立Chiplet标准联盟,正式推出Chiplet(芯粒)的通用标准“UCle”(Universal Chiplet Interconnect Express通用芯粒互连),用来打通各家芯片链接协议,构建一个开放可互操作的Chiplet生态系统。

正当业内诧异Chiplet联盟成员没有苹果、遗憾没有中国大陆芯片厂商问津时,3月14日,来自芯东西的一篇报道,透露出国内Chiplet标准即将面世的消息,国标Chiplet草案已制订完毕并有望在2022年第一季度公示,今年年底将进行《小芯片接口总线技术要求》初版标准发布,或将成为国产芯片打破制程封锁,实现弯道超车的重要引擎。

小芯片“续写”摩尔定律?

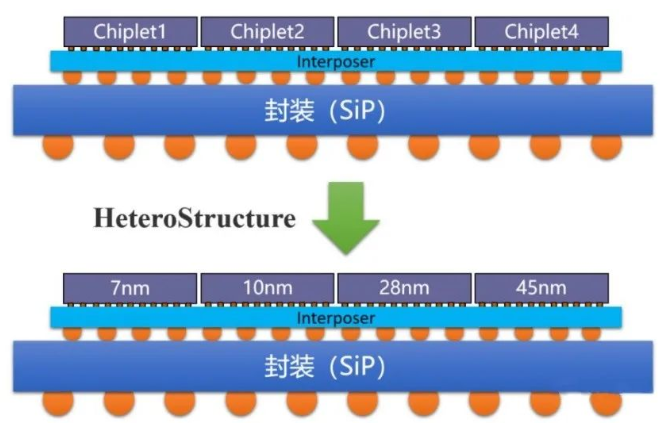

作为先进封装技术的代表,Chiplet走向了和传统SoC完全不同的道路。它将复杂芯片拆解成一组具有单独功能的小芯片单元die(裸片),通过die-to-die将模块芯片和底层基础芯片封装组合在一起,类似于搭建乐高积木,形成一个系统芯片。

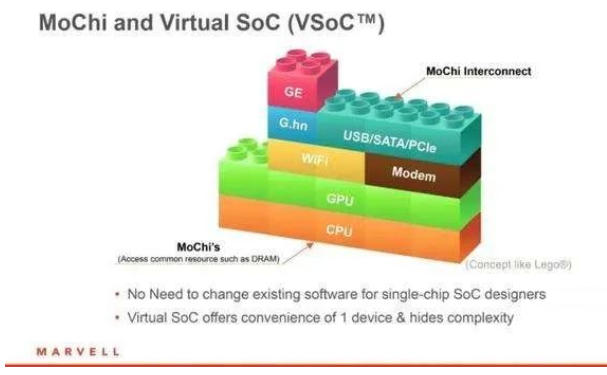

Chiplet的概念早在10余年前就被提出,Marvell创始人周秀文博士在ISSCC2015大会上提出了提出Mochi架构的概念,他认为Mochi可成为诸多应用的基础架构。几年后,这个概念开花结果,在经济优势和市场驱动下,AMD、台积电、英特尔、英伟达等芯片巨头厂商嗅到了这个领域的市场机遇,形成了现在的Chiplet。

使用Chiplet 的好处很多,以SoC为代表的集成芯片正面临经济边界和物理边界两大难题:一是先进制程工艺成本高昂,二是模拟电路、I/O 等愈来愈难以随着制程技术缩小。

而Chiplet在理论上完美补足了这两个“缺陷”,用成熟的工艺把大芯片分成小芯片,能通过量产有效改善良率,同时降低制造成本。根据研究人员分析,这项技术可以将大型7nm设计的成本降低高达25%;在5nm及以下的情况下节省成本更大。

其次,Chiplet可以降低微缩设计的复杂程度与设计成本,以电路分割的小芯片各自强化相应功能、制程技术、尺寸,最后整合在一起,以克服制程微缩的挑战。

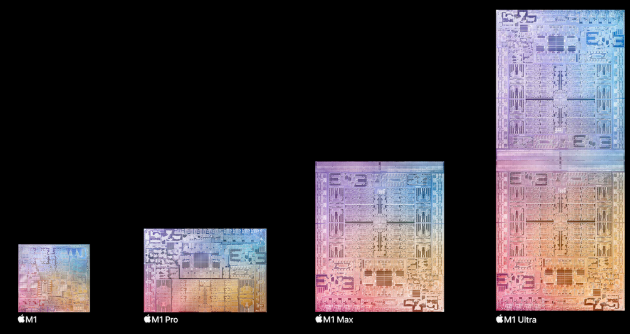

3月初Apple春季发布会上曝光的“宇宙级处理器”M1 Ultra 就是用两个M1芯片采用UltraFusion的架构封装技术完成的,搭载了1140亿个晶体管。根据苹果和台积电公布的专利论文来看,业内人士猜测,UltraFusion应是基于台积电第五代CoWoS Chiplet技术的互连架构。M1 ultra芯片充分显示了Chiplet在封装互连技术、半导体制造和电路设计上的巨大想象空间。

图源:苹果

苹果M1的工艺思路,与我国即将推出的Chiplet标准技术不谋而合。

弯道超车:中国特色的Chiplet标准

对我国半导体产业而言,Chiplet被认为是与国外差距较小的先进封装技术,被看作是后摩尔时代中国集成电路企业突破的希望,越来越多的企业与工厂加大对Chiplet的研发:华为是国内最早尝试Chiplet的一批公司,海思半导体在早期就与台积电合作过Chiplet技术,国产芯片厂商芯动科技在一款高性能服务器级显卡GPU上使用了INNOLINK Chiplet技术……

小芯片有着卓越的经济优势,但作为新生技术也面临不少挑战。困于不同架构、不同制造商生产的die之间的互连接口和协议的不同,Chiplet的研发者在设计之初就得考虑工艺制程、封装技术、系统集成、扩展传输等诸多复杂因素,这使得Chiplet的设计过程异常艰难。AMD的高级研究员Bryan Black概述了Chiplet芯片设计的九个考虑和挑战:

如何在一个系统中划分die

设计重用

管理参数变化

功率输出

连接速度

划分开销

全局时钟

die的安全

热管理

乐高玩具之所以全球风行,基础在于其积木模件的标准化,而Chiplet除了工艺设计之外的另一个难题,是die-to-die互联的标准化。

在UCle出现之前,众多芯片厂商都在“自说自话式”推广自家互联标准:如英伟达推出用于GPU的高速互联NV Link方案;Intel免费向外界授权的AIB接口总线协议;台积电也有TSMC和ARM合作搞了LIPINCON协议;AMD主张的Infinity Fabrie总线互联技术,以及用于存储芯片堆叠互联的HBM接口等等。

UCle的推行,让本在市场上互相倾轧的几大巨头开始携手抱团,可见Chiplet的商业价值与无限潜力。开始推广Chiplet标准化的时代就这样悄然来临。

面对UCle的出现,芯谋研究分析师认为,“我们要继续走好自己的路,在加速国产化替代的同时,做好应对一切冲击的准备,UCIe提供了一种可参考的产业平台机制,我们亦可以通过组建内部产业联盟的方式来优化产业分工,进一步加快国内产业发展,提高国内半导体产业对于冲击的耐受力。”

在2021年1月,国内半导体巨头华为海思牵头,与中芯国际、紫光展锐、长江存储、龙芯等国产半导体相关企业,组建了中国国产芯片联盟。2021年5月,中国计算机互连技术联盟(以下简称CCITA)在中电标协立项了Chiplet标准——《小芯片接口总线技术要求》,由国家部委和多个芯片厂商合作展开标准制定工作。

据“芯东西”报道,《小芯片接口总线技术要求》草案现已制订完毕,即将进入征求意见阶段,预计第一季度挂网公示和意见征集,第二季度完成技术验证计划制订,2022年底前完成技术验证和确定标准文本,并发布首个可用的Chiplet协议版本。

CCITA秘书长、中科院计算所研究员郝沁汾认为,“集成电路互连技术现阶段对我们国家的价值,主要是解决我们完全无法使用先进制程的问题,如采用28nm的芯片,通过chiplet的方式,使其性能和功能接近16甚至7nm工艺的芯片性能。”

解决互联标准只是第一步,在技术层面,Chiplet 还面临着来自先进封装、测试、软件配合等多个方面的挑战,郝沁汾坦言,“但是做到像PCIe、CXL这样的普及程度,还需要更长时间,也需要国内企业的支持。”

学界人士也指出,在目前芯片工艺被国际形势“卡脖子”的情况下,通过研究Chiplet先进封装,在一定程度上“绕开”被卡的技术难点,甚至实现所谓的“弯道超车”、“换道超车”是很多人自然而然的想法,但集成电路产业的积累不是短时间可以完成的,Chiplet不是救市良方也不是灵丹妙药,它不过是一种技术发展的思路而已,国内厂商要走“自研”路线,仍需打磨很长时间。

而对整个IOT行业来说,面对最大的痛点——碎片化,Chiplet为我们提供了一种组装化的思路,去面对技术碎片化、应用碎片化,当我们将这个思路扩展,用不同的物联网技术去组合搭载解决碎片化的场景,就让1+1>2成为可能。

想要了解IoT行业的最新最全市场动态,欢迎识别下方二维码报名IOTE物联网展。